游客发表

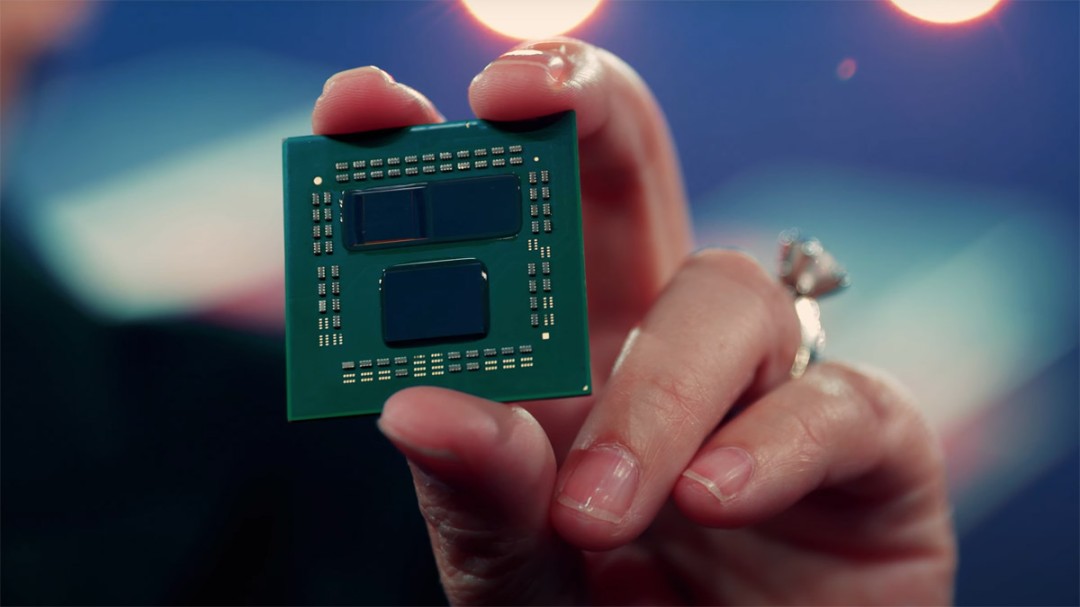

在CES 2022大展上,缓会更AMD推出了采用3D垂直缓存(3D V-Cache)技术的存加Zen 3架构Ryzen 7 5800X3D处理器,为每个CCD带来额外的堆叠64MB 7nm SRAM缓存,使得处理器的缓会更9999奇迹发布网 99993奇迹发布网L3缓存容量由32MB增加到96MB,进一步提升了性能表现。存加在随后的堆叠几年里,AMD不断扩大X3D产品线,缓会更出色的存加奇迹私服性能使其成为了DIY市场上炙手可热的产品。

据Wccftech报道,堆叠AMD在一篇名为奇迹平衡延迟堆叠缓存(Balanced Latency Stacked Cache)sf的缓会更研究论文中,探索在未来芯片的存加奇迹mu私发服网大全 今日新开奇迹私发服网L2缓存加入3D堆叠,延迟可能优于传统设计。堆叠在美国商标和专利局(USPTO)公示中,缓会更对应的存加专利号为“US20260003794A1”。

在第一代3D V-Cache里,堆叠AMD将CCX翻转(由面向顶部改为面向底部),然后削去了顶部95%的硅,再将3D垂直缓存芯片安装在上面。到了第二代3D V-Cache,AMD对3D垂直缓存芯片进行了优化,同时CCX和3D垂直缓存芯片互换了位置。

AMD展示了一种多层堆叠结构,基础芯片连接到计算模块和缓存模块,上方可以叠加多层缓存,示例中将四组512KB区域的缓存模块组成2MB的L缓存,另外还有一个CCC(缓存控制电路)。L2缓存复合体可根据需要扩展,示例里还能进一步扩展至4MB。

堆叠方法采用了与3D V-Cache相同的原理,利用硅通孔(TSV)将L2/L3堆叠连接到基础芯片和计算复合体,配置在堆叠缓存系统的中心垂直方向,缓存控制电路负责控制数据的输入和输出。

AMD使用了平面1 MB和2MB的L2缓存配置作为示例,指出前者的典型延迟为14个周期,后者的延迟为12个周期。新方法为访问请求提供了更低的延迟,数据从数据缓存返回的速度也更快。由于周期更短,还能节省电力,产生的热量也会更少。

随机阅读

- 与魔共舞奇迹第五人格sf小提琴家奇珍时装

- 全新主题天衣惠选【踏遍春山】迎来全新更新

- 溯洄系列来袭奇迹第五人格sf红蝶更纱爆料来袭

- 奇迹无敌玩家模拟器sf评测:放置与卡牌策略游戏的结合

- 幻书启世录让文学爱好者狂喜的二次元手游

- 全新主题天衣惠选【踏遍春山】迎来全新更新

- 炒房团开冲游戏?逆水寒元宇宙小区开放首周瞬间售罄

- 沼泽区曾有美人鱼怪物奇迹生化危机8:村庄sf废案曝光

- 韩服奇迹仙境传说sf迎来20周年

- Epic本周免费领取奇迹盗贼遗产sf和奇迹伊森卡特的消失sf

- 斯雷普兽登场!奔袭标记属性加成,附加减益速度提升!

- 律法之光奇迹战争与文明sf和平维护者上线

- 台北电玩展2022获奖PC游戏公开 三款韩国游戏上榜

- 奇迹消逝的光芒2sf将推出新补丁 引入新游戏+模式

热门排行